Accueil > Formation - UNITY PRO - 01/2021 > Exercice > Niveau 1 > Exercice n°3 > Exercice n°3 A > Méthode ST : Structuré

- Niveau 1

- Niveau 2

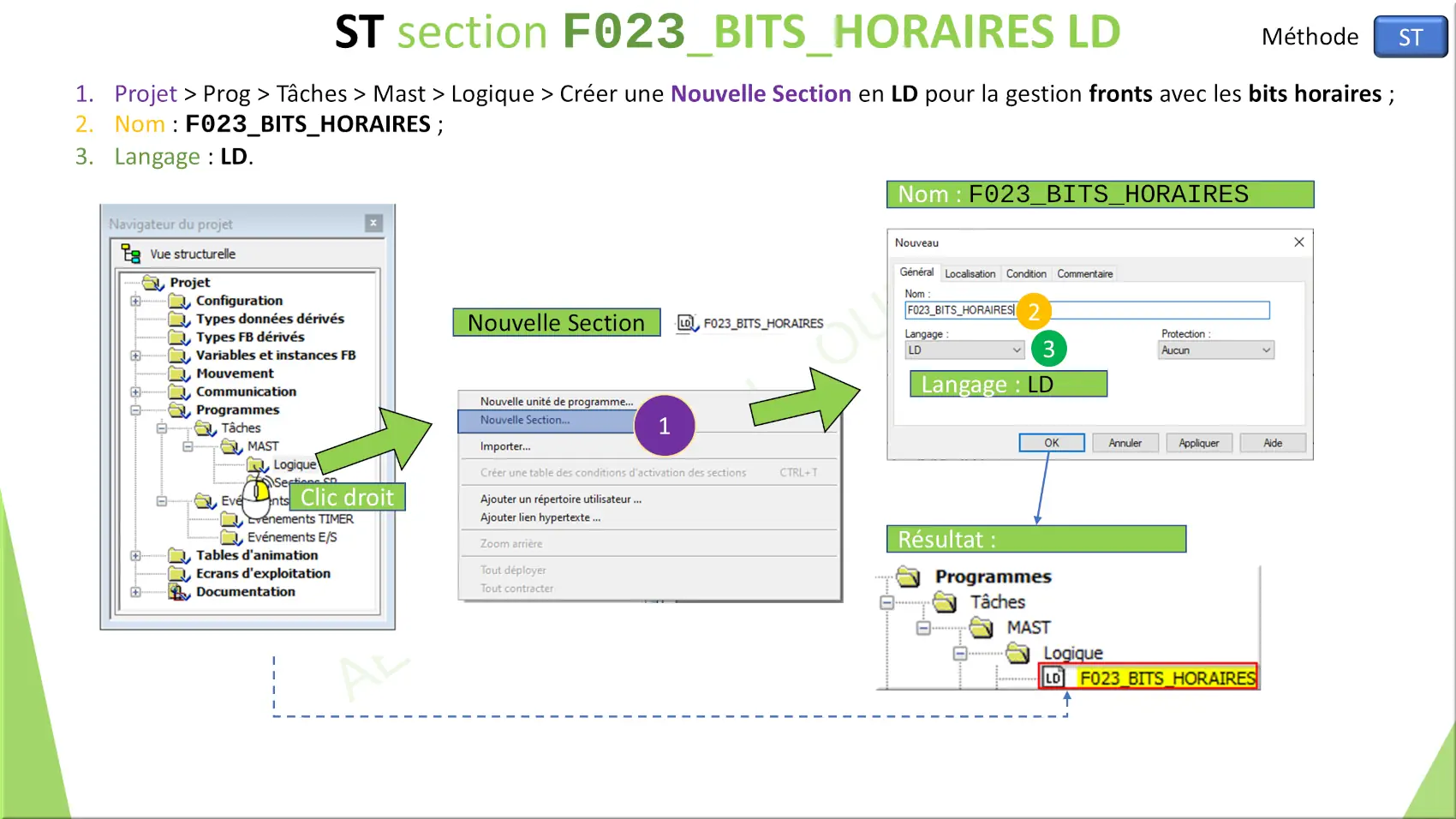

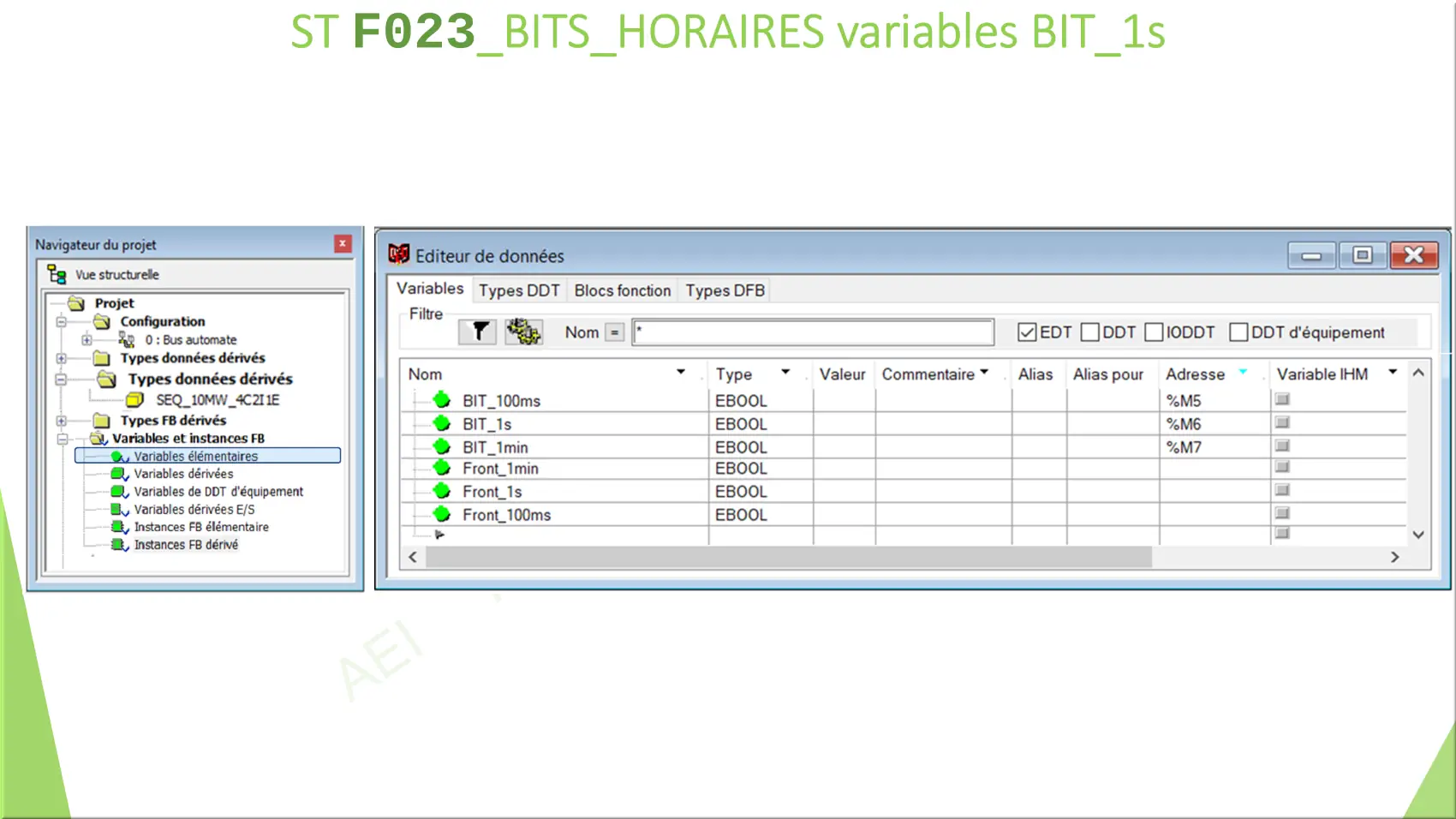

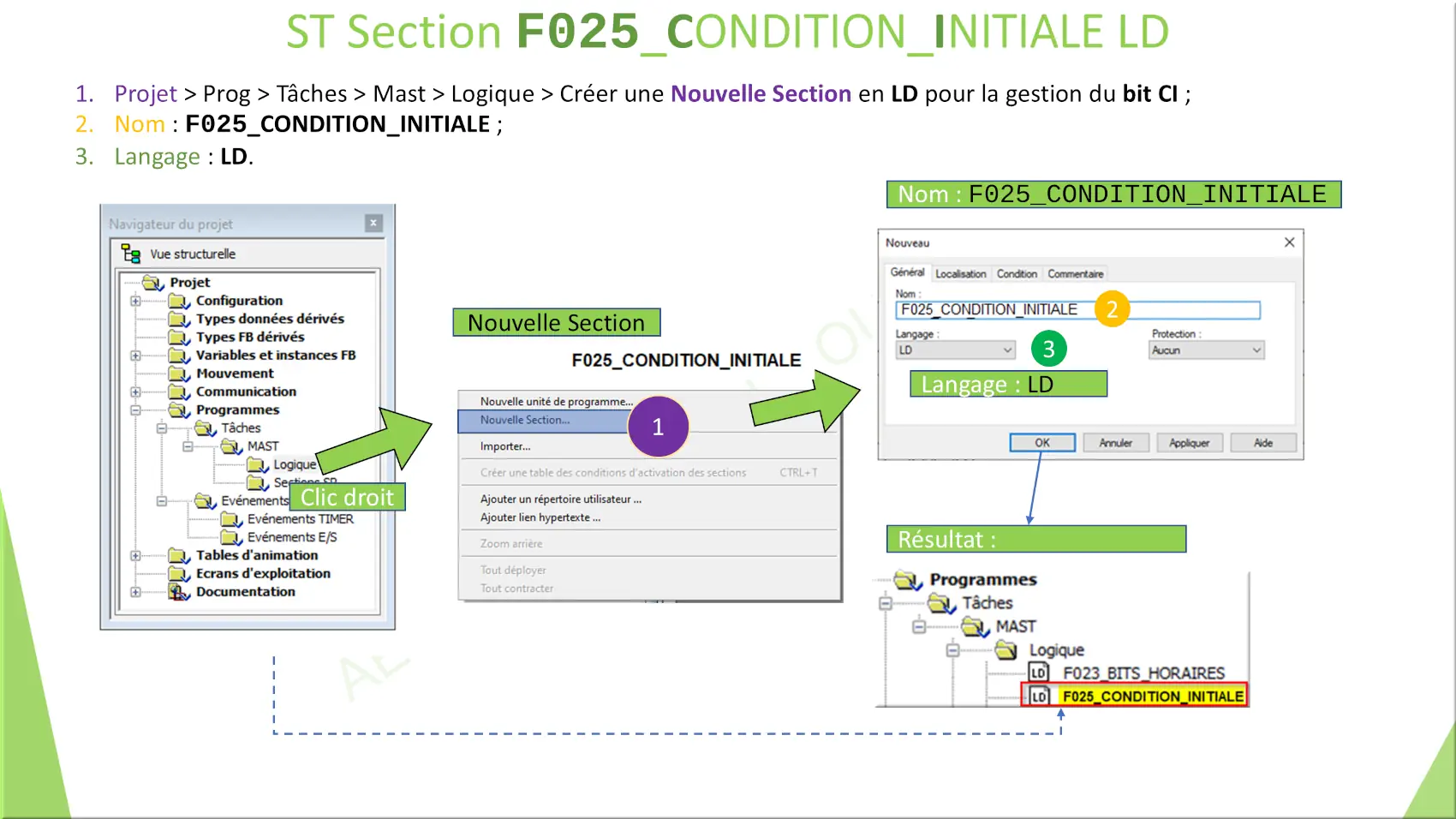

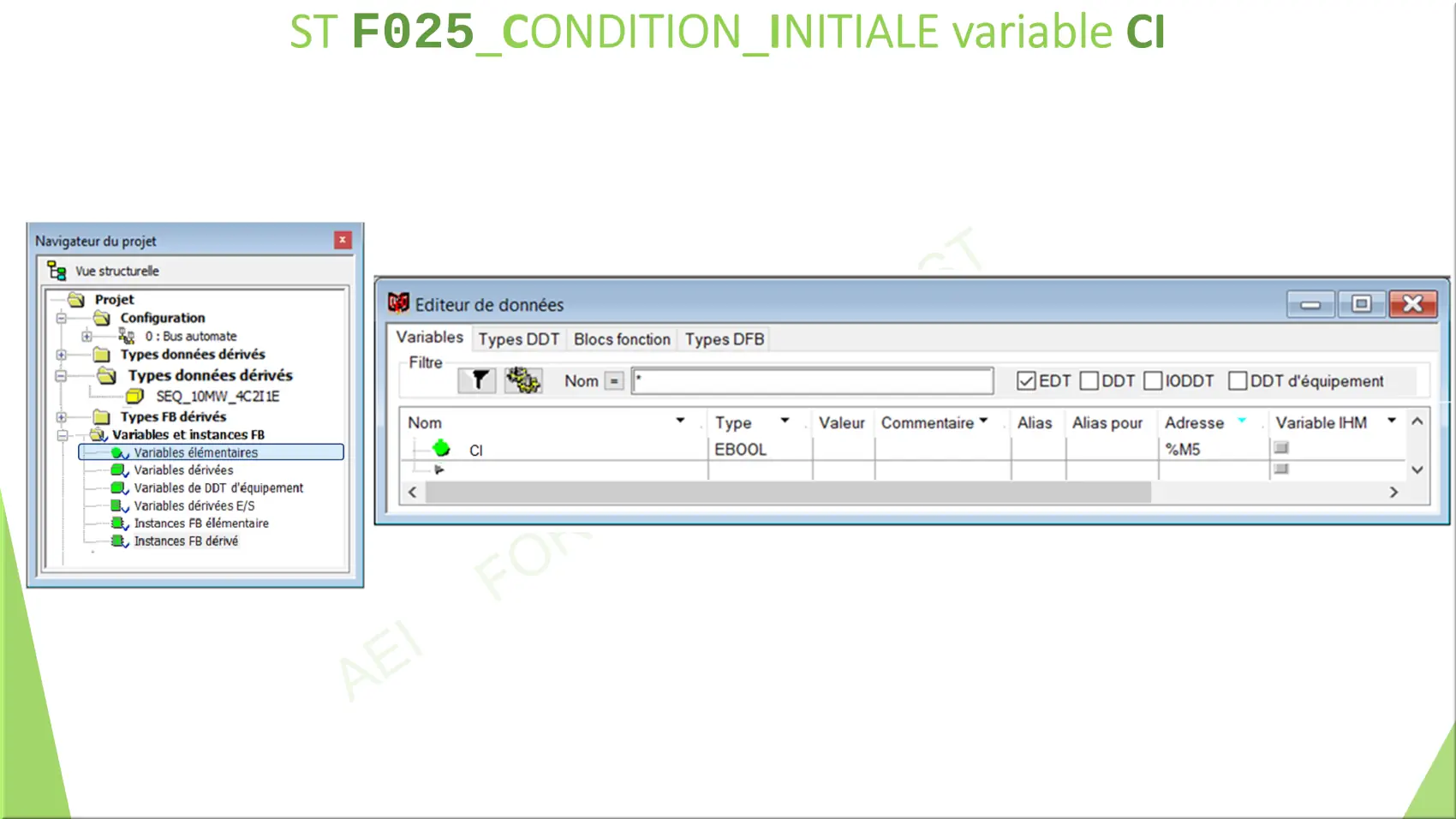

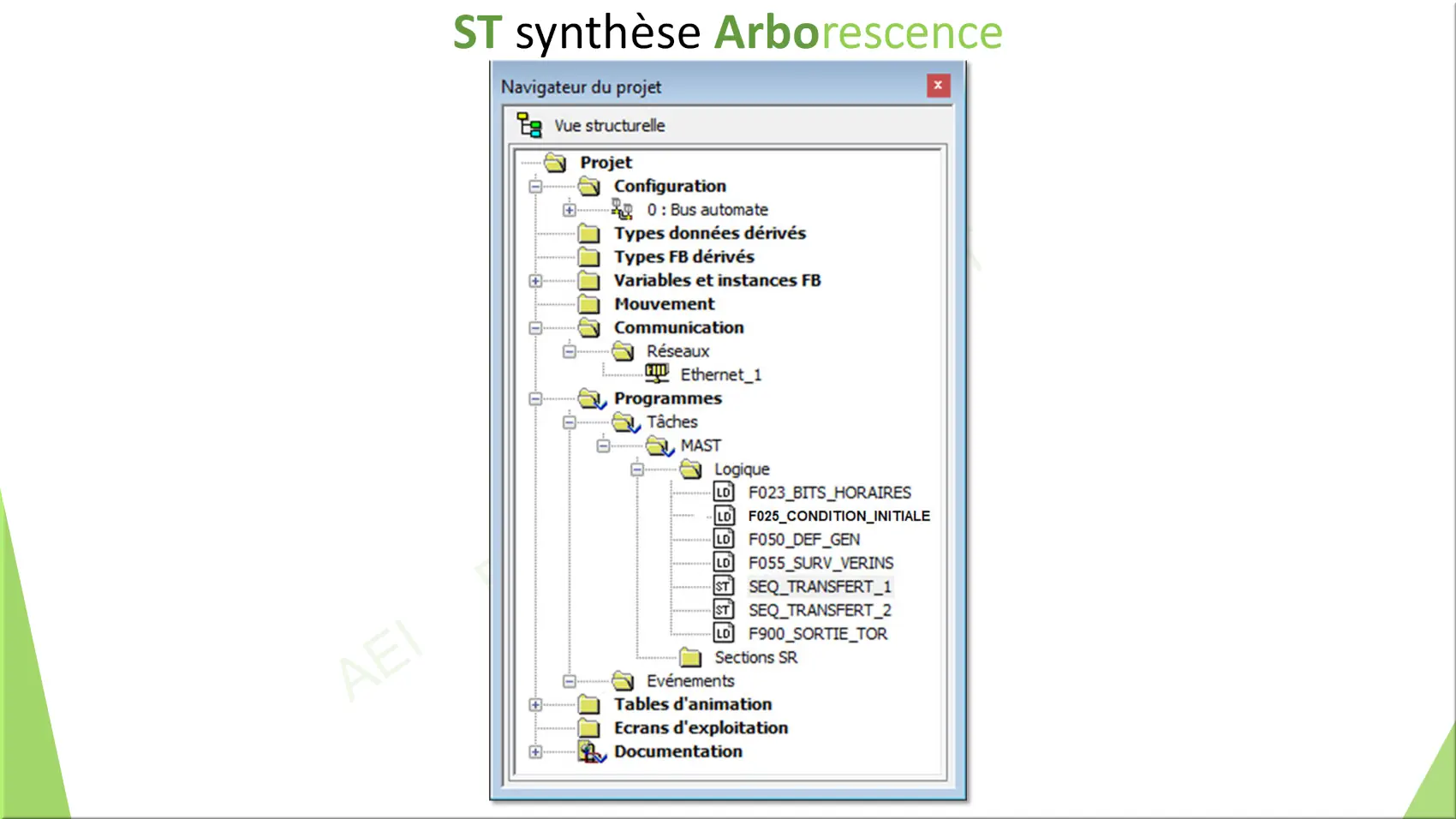

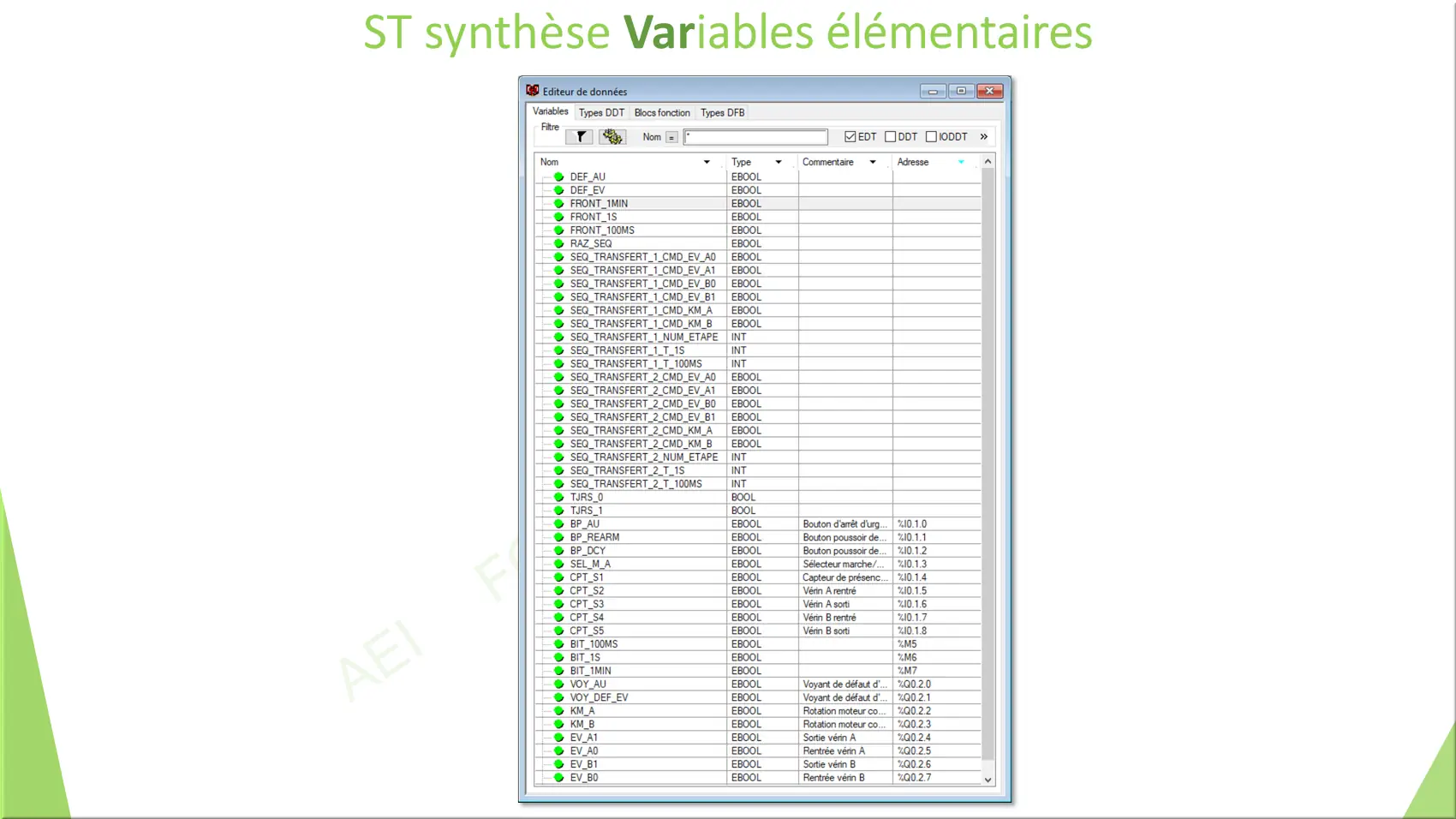

- 100. Structure Programme

- 101. Multitâche

- 102. Adressage 2

- 103. Gemma Macro

- 105. Instructions avancées

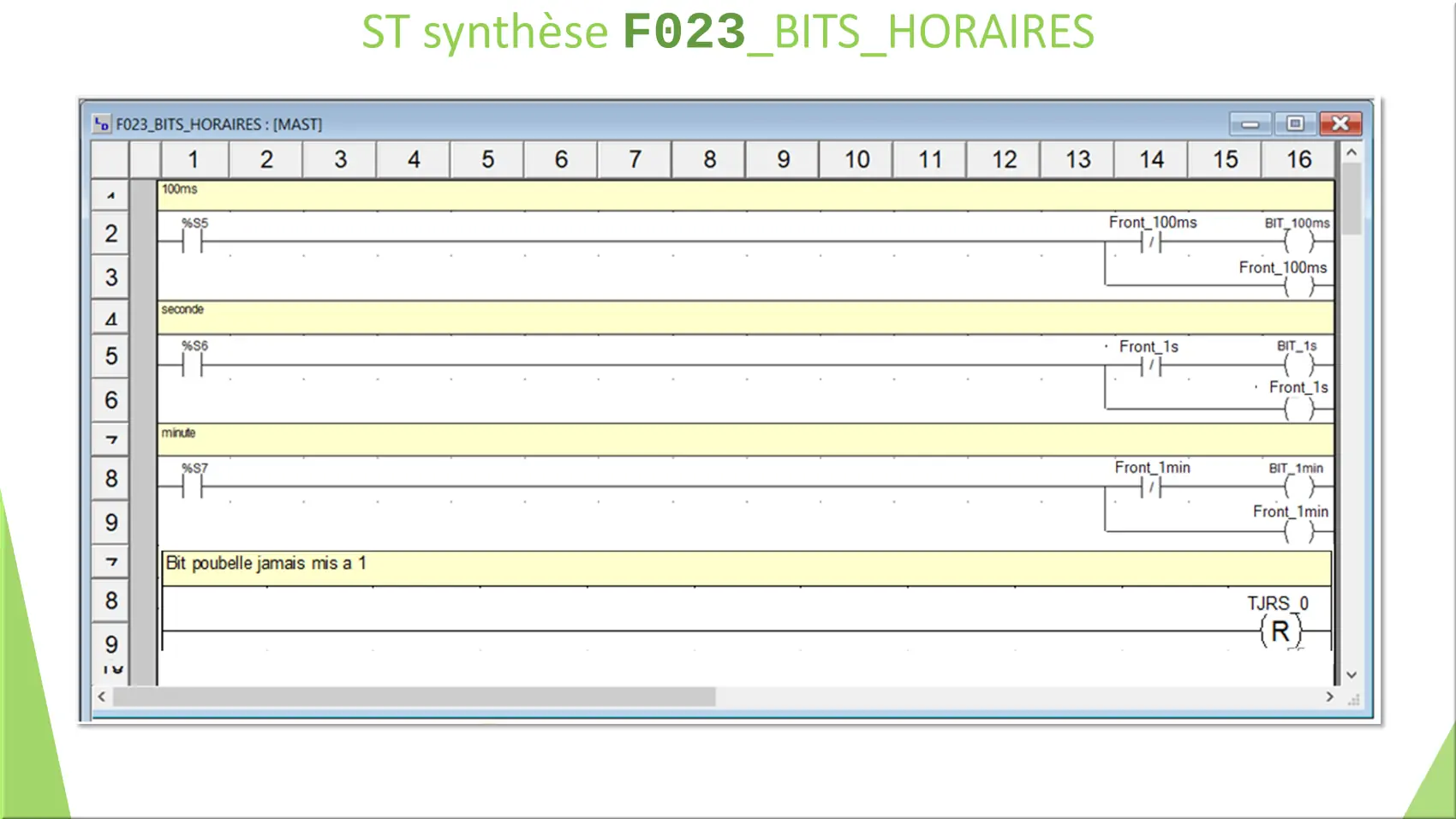

- 106. Bits et Mots Système

- 107. Bloc fonction DFB

- 108. Biblio DFB

- 109. Demande OP

- 110. Réseaux et bus

- 111. Modbus

- 112. Modbus TCP

- 114. Modbus ASi

- 115. Modbus inter API

- 118. EIP Weidmuller

- 119. E/S Déportées TM3

- 129. Comptage

- 140. IO Link

- 150. Régul

- 160. Pesage

- 180. Migration PL7 vers Unity

- Exercice

- Niveau expert